Програмне забезпечення.

Розробка двійкового суматора на мові VHDL

Бурхливий розвиток сучасної інтегральної мікросхемотехніки, особливо програмованих логічних інтегральних схем (ПЛІС), призвело до того, що алгебраїчна методологія логічного проектування перестала встигати за технологічним прогресом. Мінливість базису вимагає розробки все нових методів алгебри. Водночас прив’язка до конкретного логічного базису сильно обмежує можливості використання формальних… Читати ще >

Програмне забезпечення. Розробка двійкового суматора на мові VHDL (реферат, курсова, диплом, контрольна)

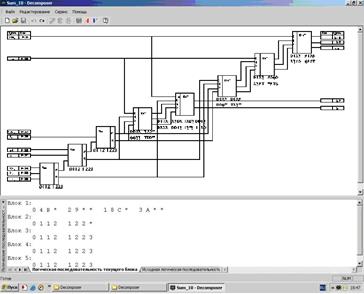

Decomposer

Бурхливий розвиток сучасної інтегральної мікросхемотехніки, особливо програмованих логічних інтегральних схем (ПЛІС), призвело до того, що алгебраїчна методологія логічного проектування перестала встигати за технологічним прогресом. Мінливість базису вимагає розробки все нових методів алгебри. Водночас прив’язка до конкретного логічного базису сильно обмежує можливості використання формальних методів синтезу. Крім того, в якості конфігуруючих логічних блоків (КЛБ) сучасних ПЛІС типу FPGA (Field Programmable Gate Arrays) використовуються логічні модулі на основі мультиплексорів або програмованих ПЗП (LUT-Look-Up Tables). У цьому випадку при проектуванні КЛС виникає завдання поділу складної схеми на більш прості частини, які можуть бути реалізовані на зазначених типах КЛБ.

Розроблений в Калужській філії МДТУ ім. Н. Е. Баумана програмний пакет Decomposer призначений для вирішення завдань автоматизованого логічного синтезу цифрових схем з використанням методів багаторівневої декомпозиції та їх реалізації на мікросхемах програмованої логіки.

Можливості САПР:

- — проведення паралельної і послідовної декомпозиції;

- — деталізація схеми до рівня двовходових блоків;

- — аналіз декомпозованої схеми.

Крім того, пакет Decomposer дозволяє отримати опис синтезованої схеми мовою VHDL, що дає можливість інтегруватися в спеціалізовані пакети програм (наприклад, WebPACK) з метою отримання файлів для «прошивки» мікросхем програмованої логіки та практичної реалізації спроектованих цифрових пристроїв.

Основні властивості VHDL :

Одне з головних властивостей — це здатність описувати апаратуру і її роботу в часі. Тому основними в VHDL є такі близькі розробнику поняття, як об'єкт проекту, інтерфейс, порт, архітектура, сигнал, атрибути сигналу, оператори паралельного присвоєння, процес та ін.

Сигнал в VHDL трактується дуже широко і може бути скалярним (цілим, речовим, бітовим і т. д.) або векторним (шинним), булевим або багатозначним. Багатозначна (реально 5-, 9- або 12- значна) логіка дає можливість виявляти за допомогою моделювання такі явища в схемах, як гонки, невизначеності на виходах схем (наприклад, асинхронного RS-тригера при заборонених значеннях вхідних сигналів), вирішувати завдання мультиплексування шини.

Рис. 2. Головне вікно програми Decomposer